Многоуровневые преобразователи: схемы, особенности применения, алгоритмы управления. Часть 3

Многоуровневый конвертер с последовательным соединением H-мостов (SCHB VSC)

Концепция этого класса многоуровневых преобразователей (MLI) состоит в последовательном соединении однофазных ячеек (рис. 1). Первая ссылка на подобную схему появилась в 1975 году, публикация новых патентов продолжается до настоящего времени. Топология SCHB VSC (для простоты будем называть ее MLI) имеет ряд преимуществ, что делает ее очень привлекательной для применения в приводах средней и высокой мощности. Поскольку в основе схемы лежит последовательное соединение стандартных однофазных ячеек, то напряжение и мощность такой системы легко масштабируются практически в неограниченных пределах. Напряжение питания DC-шины каждой H-мостовой ячейки обеспечивается отдельно.

Важное преимущество топологии MLI — возможность формирования большего числа уровней выходного напряжения с хорошим гармоническим спектром при использовании недорогих низковольтных силовых полупроводниковых ключей и конденсаторов. К недостаткам можно отнести множество силовых ключей, необходимость питания каждой ячейки от сложного и дорогостоящего «полноразмерного» трансформатора, а также относительную сложность алгоритма управления.

Однофазная ячейка (H-мост)

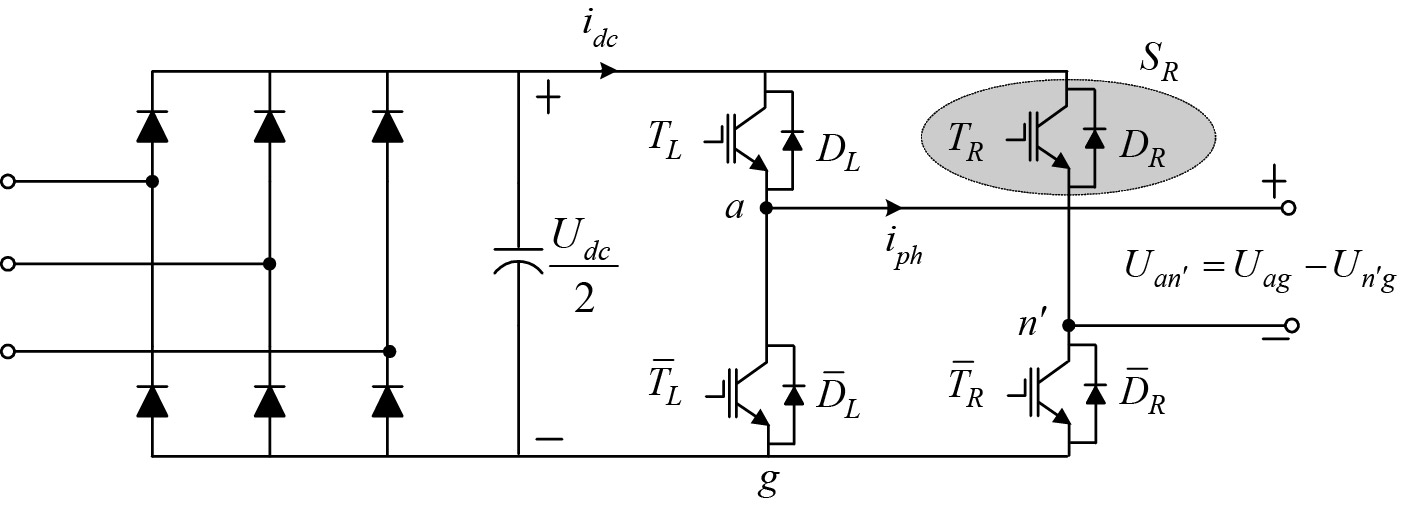

На рис. 2 показана базовая схема однофазной ячейки, лежащей в основе MLI-системы. Ячейка содержит трехфазный выпрямитель, соединенный с изолированной обмоткой трансформатора, звено постоянного тока и Н-мостовой каскад, генерирующий модулированное (ШИМ) выходное напряжение.

Коммутационные состояния

Каждая однофазная ячейка содержит два полумоста, обозначения TL и TR использованы для идентификации транзисторов и логики их управления (1 = on и 0 = off). Транзисторы в полумостовом каскаде всегда переключаются в противофазе, поэтому IGBT нижнего плеча обозначены T’L и T’R. Коммутационные положения для трех возможных состояний каждой фазной стойки приведены в таблице 1.

|

Состояние |

SL |

SR |

–SL |

–SR |

Uag |

Un`g |

Uan` |

|

Положительное «+» |

1 |

0 |

0 |

1 |

Udc/2 |

0 |

Udc/2 |

|

Нейтральное «0» |

1 |

1 |

0 |

0 |

Udc/2 |

Udc/2 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

|

Отрицательное «–» |

0 |

1 |

1 |

0 |

0 |

Udc/2 |

–Udc/2 |

Пути положительных и отрицательных фазовых токов iph показаны на рис. 3. Нулевое состояние «0» может формироваться двумя способами в зависимости от направления iph. Поэтому если включены верхние (TL, TR) или нижние IGBT (T’L, T’R), выходное напряжение приближается к нулю. В положительном «+» и отрицательном «–» состояниях ток проводят два диагональных транзистора (два активных ключа или два диода). Соответственно, H-мостовая ячейка формирует три определенных уровня напряжения.

Каждый из ключей должен блокировать напряжение DC-шины (Udc/2), максимальный ток IGBT/диода равен максимальному фазному току ![]() . Эти параметры определяют выбор номинальных характеристик силовых модулей. Распределение потерь проводимости приведено в таблице 2. Динамические потери генерируются при изменении коммутационных состояний транзисторов и диодов.

. Эти параметры определяют выбор номинальных характеристик силовых модулей. Распределение потерь проводимости приведено в таблице 2. Динамические потери генерируются при изменении коммутационных состояний транзисторов и диодов.

|

Состояние |

TL |

DL |

TR |

DR |

–TL |

–DL |

–TR |

–DR |

|

Положительная фаза тока |

||||||||

|

«+» (Uag= Udc/2) |

× |

|

|

|

|

|

× |

|

|

«0» (Uag = 0) |

× |

|

|

× |

|

|

|

|

|

|

|

|

|

|

× |

× |

|

|

|

«–» (Uag= –Udc/2) |

|

|

|

× |

|

× |

|

|

|

Отрицательная фаза тока |

||||||||

|

«+» (Uag= Udc/2) |

|

× |

|

|

|

|

|

× |

|

«0» (Uag=0) |

|

|

|

|

× |

|

|

× |

|

|

× |

× |

|

|

|

|

|

|

|

«–» (Uag= –Udc/2) |

|

|

× |

|

× |

|

|

|

Два комплементарных ключа в каждой стойке (TR, T’R) или (TL, T’L) участвуют в процессах коммутации (+ → 0) и (0 → –). Для положительного фазового тока iph > 0 коммутация (+ → 0) инициируется выключением TL в первой фазной стойке, в результате чего ток переходит от TL к DL. Транзистор T’R остается включенным, и только два комплементарных ключа в первой стойке участвуют в этом цикле коммутации. Большую часть потерь выключения генерирует TL.

Во второй фазной стойке коммутация (+ → 0) инициируется выключением T’R, в результате чего ток переходит от T’R к DR, транзистор TL остается включенным. Только два комплементарных ключа во второй стойке участвуют в этом цикле коммутации (TR, T’R). Основные потери выключения генерируются T’R. При реверсной коммутации (0 → +) все процессы идут в обратном порядке. Например, во второй стойке сначала отключается TR, а затем после «мертвого времени» включается T’R. Транзистор T’R генерирует потери включения, а диод DR — потери восстановления.

Процесс коммутации проиллюстрирован на рис. 4, где токовый путь активного ключа показан жирной линией, пассивного ключа — пунктирной линией. Устройства, генерирующие потери, выделены окружностями. Коммутация (0 → –) в первой стойке начинается с активного выключения TL, что приводит к прохождению тока через D’L. Диод DR уже находится в проводящем состоянии, TL генерирует потери выключения. При реверсной коммутации (– → 0) все процессы идут в обратном порядке. T’L выключается, затем TL открывается после «мертвого времени».

Рис. 4. Коммутация и потери переключения в Н-мостовой ячейке:

а) и б) для положительного тока нагрузки;

в) и г) для отрицательного тока нагрузки

После срабатывания TL фазный ток коммутируется от D’L обратно к TL. Диод D’L закрыт, таким образом он берет на себя блокирующее напряжение и генерирует потери восстановления, а TL — потери включения.

Во второй стойке коммутация (0 → –) инициируется активным запиранием T’R, что переключает ток на DR. Диод D’L уже открыт, T’R генерирует потери выключения. В реверсном режиме (– → 0) все процессы идут в обратном порядке: TR выключен, T’R открывается после «мертвого времени». После его срабатывания фазный ток переходит от DR обратно к T’R. Диод DR выключается, берет на себя блокирующее напряжение и генерирует потери восстановления (рис. 4б). Процессы переключения на участке отрицательного тока проиллюстрированы на рис. 4в, г. Распределение коммутационных потерь сведено в таблицу 3.

|

Состояние |

TLx |

DLx |

TRx |

DRx |

–TLx |

–DLx |

–TRx |

–DRx |

|

Положительная фаза тока |

||||||||

|

+ ↔ 0 |

|

|

|

× |

|

|

× |

|

|

× |

|

|

|

|

× |

|

|

|

|

0 ↔ – |

× |

|

|

|

|

× |

|

|

|

|

|

|

× |

|

|

× |

|

|

|

Отрицательная фаза тока |

||||||||

|

+ ↔ 0 |

|

× |

|

|

× |

|

|

|

|

|

|

× |

|

|

|

|

× |

|

|

0 ↔ – |

|

|

× |

|

|

|

|

× |

|

|

× |

|

|

× |

|

|

|

|

Центрированная синусоидальная модуляция

Каждая ячейка модулируется синусоидальным сигналом с добавлением 1/6 третьей гармоники (рис. 5). Процесс коммутации одной ячейки (полумост) задается сравнением соответствующих несущих (Utri,1 и Utri,2), сдвинутых по фазе на TC/2 (180°), и опорного сигнала Ucon. Таким образом, за один период несущего сигнала происходит четыре переключения. Как показано на рис. 5, сравнение Ucon и Utri,1 формирует следующие сигналы управления ключами в первой стойке:

Рис. 5. Формы сигналов в Н-мостовой ячейке:

а) сигнал управления Ucon, треугольные сигналы Utri,1 и Utri,2;

б) выходное напряжение стойки а — Uag;

в) выходное напряжение стойки n’ — Un’g;

г) напряжение нагрузки Uan’

Для формирования импульсов управления второй стойкой Utri,2 сравнивается с тем же опорным сигналом:

Благодаря наличию антипараллельных диодов форма вышеупомянутых сигналов не зависит от направления фазного тока iph. Выходные напряжения стоек а и n’ относительно отрицательной DC-шины (g) показаны на рис. 5б и 5в соответственно. Выходной сигнал H-моста (рис. 2), показанный на рис. 5г, состоит из трех уровней: ±Udc/2 и 0.

Поскольку две стойки H-моста управляются независимо, первая гармоника несущей в выходном напряжении имеет двойную частоту (f1Cb = 2fC). Это преимущество проявляется в улучшении гармонического спектра, как показано на рис. 6. Если выбрать четный коэффициент частотной модуляции mf, то выходные сигналы любой из стоек Uag и Un’g на основной частоте смещаются на 180° относительно друг друга. Таким образом, гармонические компоненты на частоте ШИМ в фазных стойках имеют одинаковую фазу, поскольку выходы смещены на 180°, а коэффициент mf — четный. Это приводит к подавлению боковых гармоник частоты ШИМ в выходном сигнале.

Кроме того, использование такого режима модуляции создает меньшие пульсации в DC-шине. Когда оба верхних ключа открыты, выходное напряжение равно нулю, а ток циркулирует в контуре (TL, DR) или (DL, TR) в зависимости от направления iph. В течение этого интервала времени ток idc равен нулю. Аналогичное состояние наблюдается, когда открыты нижние ключи TL и TR.

Трехфазный двухуровневый Н-мостовой конвертер (2L-H-Bridge)

Увеличение количества фаз конвертера может быть реализовано простым добавлением H-мостовых ячеек. Упрощенная схема трехфазного двухуровневого Н-мостового преобразователя показана на рис. 7. Он содержит 12 однонаправленных активных ключей с обратными диодами.

Коммутационные состояния

Для того чтобы сформировать три уровня напряжения в каждой фазе, два из четырех ключей должны быть открыты в любой момент времени. Обозначения SLx и SRx используются для идентификации транзисторов в каждой фазе (x = a, b, c). Поскольку они всегда коммутируются попарно, комплементарные IGBT обозначены как S’Lx и S’Rx. Коммутационные положения ключей для трех возможных состояний каждой фазы такие же, как для однофазного H-моста. Распределение потерь проводимости и переключения также аналогично (табл. 2, 3).

Центрированная синусоидальная модуляция

Способ модуляции остается таким же, как описан выше для однофазного H-моста, формирование импульсов управления трехфазным инвертором показано на рис. 8. Опорные сигналы в трехфазной 2L-H-мостовой схеме смещены на 120°, поэтому управляющие сигналы для каждой фазы формируются отдельно путем сравнения опорного сигнала Ucon,x (x=a, b, c) с треугольными несущими Utri1, Utri2 (они сдвинуты на TC/2).

Рис. 8. Формы сигналов в трехфазной 2L-Н-мостовой ячейке:

а) сигнал управления Ucon,x и треугольные сигналы Utri,1 и Utri,2;

б) импульсы управления затвором;

в) выходное фазное напряжение;

г) выходное линейное напряжение

Таким образом, происходит четыре коммутации на фазу в течение одного периода несущего сигнала. Для генерации импульсов управления затвором может использоваться такой же алгоритм, как и для однофазного H-моста:

Ucon,x > Utri1 (TLx:on, T’Lx:off), Ucon,x > Utri2 (TRx:on, T’Rx:off) → Uxn’ = Udc/2.

Ucon,x< Utri1 (TLx:off, T’Lx:on), Ucon,x< Utri2 (TRx:on, T’Rx:off) → Uxn’ = –Udc/2.

Иначе

→ Uxn’ = 0.

Выходные сигналы трехфазного 2L-H-моста (рис. 7) показаны на рис. 8. Фазные напряжения (например, Uan’) содержат три уровня: ±Udc/2 и 0 (рис. 8в), линейные (например, Uab) — содержат пять уровней: ±Udc, ±Udc/2 и 0 (рис. 8г).

Гармонические спектры фазного и линейного напряжения показаны на рис. 9a и 9б, соответственно (для mf = 15). Как и в однофазном H-мосте, первые гармоники несущей в 2L-H-мостовой схеме наблюдаются на двойной частоте коммутации (f1Cb = 2fC).

Рис. 9. Гармонический спектр трехфазной 2L-Н-мостовой ячейки:

а) фазное выходное напряжение;

б) линейное выходное напряжение

Конвертер напряжения с последовательным соединением 2L-H-мостовых ячеек (SC2LHB VSC)

В традиционных топологиях схем, таких как 2L-VSC или 3L-NPC VSC, приборы с максимальной блокирующей способностью (например, 6,5 кВ IGBT) должны соединяться последовательно для достижения необходимого линейного выходного сигнала (Ull > 3,3 кВ и Ull > 4,16 кВ). Концепция схемы с последовательным соединением двухуровневых Н-мостов (SC2LHB VSC) показана на рис. 10. Впервые такой конвертер был запатентован компанией Robicon.

Схема SC2LHB VSC широко используется в средневольтовых приводах, источниках питания, энергетических системах переменного тока. Характеристики системы SC2LHB VSC определяются количеством отдельных H-мостовых ячеек и уровнем их выходного сигнала. Амплитуда «ступеньки» выходного напряжения сравнительно мала и равна величине Vdc одного H-моста (например, 600 В для Vin = 460 В).

Для формирования определенного номинального напряжения MV-диапазона выходы однофазных низковольтных ячеек (например, на базе IGBT 17-го класса) соединяются последовательно. Общее «виртуальное» напряжение Udc,tv будет определяться количеством последовательно соединенных Н-мостов:

Udc,tv = 2×p×Udc,HB.

При использовании одинаковых ячеек с равным значением Udc,HB преобразователь синтезирует выходное фазное напряжение (Uan’, Ubn’, Ucn’):

Uxn’ = U1xn’+ U2xn’+…Upxn’.

Количество уровней в фазном сигнале — N = 2p + 1, в линейном сигнале — Nll = 2N – 1. Для общепромышленных стандартных напряжений 2,3–7,2 кВ число ячеек составляет 2–5. При p = 2 схема на рис. 10 формирует пять определенных фазных уровней (N = 5). При соединении 3, 4 и 5 ячеек фазный сигнал состоит из 7, 9 и 11 уровней соответственно.

Для управления каждой ячейкой необходимы две треугольные несущие, как и в однофазном H-мосте. В отличие предыдущего случая пара несущих должна иметь фазовый сдвиг 180°/p, первая H-мостовая ячейка считается «опорной». При таком способе модуляции эквивалентная частота первой гармоники несущей в выходном напряжении:

f1Cb=2×p×fC,

где fC — несущая частота.

Благодаря наличию нескольких уровней напряжения и высокой частоте f1Cb амплитуда гармоник в выходном сигнале достаточно низкая, поэтому его фильтрация намного проще. Каждый дополнительный уровень означает еще одну «степень свободы» в улучшении гармонического состава.

Для повышения напряжения конвертера следует увеличить число последовательных H-мостов. Поскольку выходной сигнал равномерно распределен между однофазными ячейками, появляется возможность подключения одного или нескольких дополнительных Н-мостов. В случае отказа это позволяет, например, закоротить выход неисправного узла. Причем привод продолжает работать с номинальными параметрами. Максимальное входное и выходное напряжение каждой ячейки равно мгновенному значению Vdc, как видно на рис. 2, поэтому емкость DC-шины можно рассматривать как большой снаббер для всех ключей.

Все однофазные ячейки обеспечивают одинаковый ток на базовой выходной частоте, поэтому они имеют равную мощность, а также простую и модульную концепцию управления. Хотя в H-мостовой схеме можно применять различные низковольтные полупроводниковые приборы, лучшим выбором являются LV-IGBT благодаря пренебрежимо малым потерям на управление и хорошим характеристикам переключения. Как правило, в MV MLI-системах используются недорогие IGBT 17-го класса. Подобные инверторы с 2–5 ячейками на фазу формируют линейное напряжение 2,3; 3,3; 4,16 и 6 кВ. Другим важным преимуществом такого решения является минимальное значение синфазного напряжения и потенциально низкие перепады dv/dt в выходном сигнале.

Питание DC-шины каждой H-мостовой ячейки должно формироваться независимо. Для этой цели выпрямители ячеек подключаются к изолированным вторичным обмоткам специального многоуровневого трансформатора. Такой трансформатор намного сложнее и дороже обычного, но выполняет несколько очень важных функций. Во-первых, с его помощью любое синфазное напряжение не воздействует на изоляцию двигателя. Во-вторых, благодаря фазовому сдвигу ap = 360°/6p между вторичными обмотками удается подавить большую часть гармонических токов, создаваемых отдельными силовыми ячейками. Таким образом, форма первичных токов будет близкой к синусоидальной.

Импеданс трансформатора сознательно выбирается большим, чем обычно, чтобы ограничить пусковые токи и уменьшить амплитуду гармоник. Благодаря хорошему гармоническому составу сетевых токов можно уменьшить входной фильтр, что частично компенсирует высокую стоимость трансформатора. В таблице 4 приводится сравнение основных характеристик системы при различном количестве H-мостовых ячеек на фазу.

|

Количество последовательных Н-ячеек, p |

2 |

3 |

4 |

5 |

p |

|

Количество уровней в фазном напряжении, N |

5 |

7 |

9 |

11 |

2p+1 |

|

Количество уровней в линейном напряжении, Nll |

9 |

13 |

17 |

21 |

4p+1 |

|

Количество DC-конденсаторов |

6 |

9 |

12 |

15 |

3p |

|

Смещение фаз между обмотками трансформатора, αp |

30° |

20° |

15° |

12° |

60/p |

|

Количество несущих |

4 |

6 |

8 |

10 |

2p |

|

Смещение фаз между несущими |

90° |

60° |

45° |

36° |

180/p |