IGBT и MOSFET: основные концепции и пути развития. Часть 2. MOSFET

Поскольку сопротивление «сток–исток» RDS(on) открытого канала низковольтных MOSFET состоит из индивидуальных сопротивлений отдельных ячеек с разбросом 5–30%, у выпускаемых ранее транзисторов более чем 90% ячеек имели превышенное обратное напряжение, обусловленное сопротивлением эпитаксиальной n—-области. Зависимость сопротивления открытого канала MOSFET от напряжения пробоя V(BR)DSS описывалась выражением:

RDS(on) = k × V(BR)DSS2,4…2,6,

где k — материальная константа (например, k = 8,3×10-9 на 1 см2 площади кристалла), то есть прямое напряжение VDS(on) = ID × RDS(on) (ID — ток стока) для транзисторов с обратным напряжением свыше 400 В было намного больше, чем у IGBT аналогичного токового диапазона.

Принцип «компенсации», использованный в разработанных в 1999 г. транзисторах с «суперпереходом» (Superjunction MOSFET), позволил разрушить соотношение между обратным напряжением и степенью легирования n—-области и существенно снизить сопротивление канала высоковольтных полевых транзисторов. Как показано в [11], теперь зависимость RDS(on) выглядит следующим образом:

RDS(on) = k × V(BR)DSS1,3.

Для практических задач чисто омическая выходная характеристика MOSFET намного предпочтительнее «биполярной» характеристики, имеющей пороговый уровень напряжения. Важным преимуществом униполярной полевой структуры перед биполярной является отсутствие эффекта накопления заряда, поскольку основные носители в них отвечают исключительно за перенос заряда, что позволяет обеспечить предельно малое время коммутации.

На практике свойства силовых MOSFET-модулей очень сильно зависят от паразитных элементов, неизбежно присутствующих в кристаллах и соединительных цепях. Для анализа данных факторов необходимо рассмотреть эквивалентную схему MOSFET, представленную на рис. 10.

Описание и физический смысл паразитных элементов структуры MOSFET даны в таблице 1.

|

Обозначение |

Наименование |

Физический смысл |

|

CGS |

Емкость «затвор–исток» |

Образована перекрывающей металлизацией областей затвора и истока; зависит от напряжения «затвор–исток»; не зависит от напряжения «сток–исток». |

|

CDS |

Емкость «сток–исток» |

Емкость перехода между n—-дрейфовой зоной и p-кармана; зависит от площади поверхности ячейки, напряжения пробоя и напряжения «сток–исток». |

|

CGD |

Емкость «затвор–сток» |

Емкость Миллера; образована перекрывающимися областями затвора и n—-дрейфовой зоной. |

|

RG |

Внутреннее сопротивление затвора |

Сопротивление поликристаллического кремния; как правило, необходима установка индивидуальных резисторов каждому параллельному кристаллу для выравнивания токов. |

|

RD |

Сопротивление стока |

Сопротивление n—-зоны; основная часть сопротивления открытого канала MOSFET. |

|

RW |

Боковое сопротивление р-кармана |

Сопротивление «база–эмиттер» паразитного биполярного n-p-n-транзистора. |

Если не учитывать внутренние емкости и сопротивления, то эквивалентная схема может быть представлена как «идеальный MOSFET» с n-p-n-транзистором в области затвора: n+-область истока (эмиттер)/р+-карман (база)/n-дрейфовая зона (коллектор) с боковым резистором р+-кармана под эмиттером в качестве сопротивления «база–эмиттер» RW. Этот резистор и переход «база–коллектор» паразитного биполярного транзистора образуют антипараллельный (тельный) диод, обеспечивающий обратную проводимость MOSFET.

Статические характеристики

На рис. 11 показаны выходные характеристики MOSFET, имеющего внутренний инверсный диод, и переходная характеристика диода.

К стационарным режимам коммутации относятся прямое выключенное состояние и лавинный пробой. Если к транзистору приложено положительное напряжение «сток–исток» VDS, а сигнал «затвор–исток» VGS находится ниже порогового уровня VGS(th), то транзистор проводит только очень малый ток утечки IDSS. С увеличением VDS ток IDSS сначала немного возрастает. Когда напряжение «сток–исток» превышает предельно допустимый уровень VDSS, происходит лавинный пробой в PIN-переходе: p+-карман/n—-дрейфовая зона/n+-эпитаксиальный слой. По физике процесса величина V(BR)DSS примерно соответствует напряжению пробоя VCER паразитного биполярного n-p-n-транзистора, образованного следующими слоями MOSFET-структуры: n+-область истока (эмиттер)/p+-карман (база)/n—-дрейфовая зона/n+-эпитаксиальный слой в области стока (коллектор).

Ток, генерируемый при лавинном пробое в «коллектор-базовом» диоде, может привести к открыванию биполярного транзистора и разрушению MOSFET-структуры. Области базы и эмиттера почти закорочены металлизацией эмиттера, между ними нет ничего, кроме бокового сопротивления р+-кармана. С помощью различных технологических мер, к которым относятся уменьшение размера ячеек, равномерное распределение поля в ячейках, снижение сопротивления р+-карманов, а также оптимизация внешней структуры, удается добиться очень низкого тока пробоя в ячейках, что позволяет (при определенных условиях) исключить защелкивание паразитной биполярной структуры. Для таких кристаллов MOSFET, имеющих повышенную стойкость к пробою, в документации определяется допустимый уровень лавинной энергии ЕА, нормируемый для одиночного импульса или периодической нагрузки (в этом случае он ограничен предельной температурой кристалла).

Гарантировать абсолютно симметричное распределение токов параллельных чипов, входящих в состав силового ключа, невозможно, поэтому норма ЕА, определяемая для одного кристалла, относится ко всему модулю.

Включенное состояние (1 квадрант)

Состояние прямой проводимости при приложении положительного напряжения VDS и положительном направлении тока стока ID определяет две области характеристической кривой: активную и омическую.

Активная зона характеристики

При большом превышении напряжением «затвор–исток» порогового уровня VGE(th), относительно высокая доля этого сигнала окажется приложенной к каналу вследствие токового насыщения (горизонтальный участок выходной характеристики). Ток стока ID управляется напряжением VGS. Параметром переходной кривой (рис. 11б) является прямая проводимость gfs, определяемая как

gfs = DID/DVGS = ID/(VGS–VGS(th)).

Прямая проводимость растет пропорционально ID и VDS и падает с увеличением температуры кристалла. В режиме коммутации модулей, содержащих несколько параллельных чипов, работа в активной области наблюдается только при включении и выключении. Стационарная работа в этой зоне недопустима, поскольку пороговое напряжение VGS(th)снижается с ростом температуры, т. е. даже небольшая разница характеристик кристаллов может привести к «тепловому убеганию».

Омическая зона характеристики

Данная область (наклонные участки выходной характеристики) соответствует включенному состоянию, при котором величина тока ID определяется только внешними цепями нагрузки. Поведение ключа при этом характеризуется сопротивлением открытого канала RDS(on), определяемым по отношению приращений напряжения VDS и тока стока ID. Величина RDS(on) зависит от сигнала управления VGS и температуры кристалла. В диапазоне рабочих температур MOSFET сопротивление открытого канала почти удваивается при нагреве от +25 до +125 °С.

Инверсный режим (3 квадрант)

В инверсном режиме MOSFET приобретает диодную характеристику при напряжении отсечки VGS(th) (рис. 11). Такое поведение обусловлено наличием паразитного диода в структуре, прямое падение напряжения образуется на переходе «коллектор–(исток)–база–(сток)–p-n-переход». Биполярный ток, проходящий через диод, определяет поведение MOSFET в инверсном режиме работы, когда канал закрыт (рис. 12а).

Рис. 12. Инверсный режим MOSFET [12]:

а) закрытый канал (биполярный ток);

б) открытый канал и низкое отрицательное напряжение VDS (униполярный ток);

в) открытый канал и высокое отрицательное напряжение VDS (комбинированный характер тока)

Динамические характеристики

Динамические свойства (скорость переключения, потери) модулей MOSFET зависят от особенностей их структуры, величины паразитных емкостей переходов и сопротивления выводов. В отличие от «идеального» ключа, контролируемого по изолированному затвору без потерь мощности, на управление реального MOSFET расходуется энергия, необходимая для перезаряда входных емкостей. Очевидно, что мощность управления зависит от величины этих емкостей и частоты коммутации.

Кроме того, на процесс переключения оказывают влияние паразитные индуктивности силовых соединений внутри транзистора и внешних цепей коммутации. Их наличие приводит к образованию выбросов напряжения при выключении, а также осцилляций на паразитных контурах.

Поведение MOSFET-ключей в импульсном режиме работы может быть проанализировано с помощью эквивалентной схемы:

- Когда транзистор отключен, емкость CGD мала и примерно равна CDS.

- При включении транзистора емкость CGD быстро увеличивается с того момента, когда сигнал управления VGSпревышает напряжение «сток–исток», причиной этого является инверсия слоя под областью затвора.

- В технических характеристиках, как правило, указывается величина емкостей Ciss, Cres, Coss выключенного транзистора (таблица 2).

|

Входная емкость |

Ciss = CGS+CGD |

|

Обратная емкость (Миллера) |

Cres = CGD |

|

Выходная емкость |

Coss = CGD+CDS |

Значения малосигнальных емкостей MOSFET не имеют особого практического значения, поскольку они очень сильно зависят от рабочего напряжения (это было подробно описано ранее). Поведение MOSFET в режиме «жесткой» коммутации активно-индуктивной нагрузки с непрерывным током (когда постоянная времени нагрузки L/R намного больше периода рабочей частоты) описано ниже. Основные эпюры токов и напряжений по аналогии с процессами, рассмотренными ранее для IGBT, показаны на рис. 13.

Кроме «неидеальности» параметров транзисторов и диодов, на потери переключения и положение рабочей точки заметное влияние оказывают пассивные распределенные элементы цепи коммутации.

Включение

Как показано на рис. 13, напряжение «сток–исток» силового MOSFET падает до уровня насыщения примерно за 10 нс, его величина определяется по формуле VDC(on) = ID × RDS(on).

На интервале времени 0–t1 транзистор остается заблокированным. Ток затвора IG начинает протекать при появлении сигнала управления, он заряжает емкость CGS до тех пор, пока заряд на ней не достигнет уровня QG1. Напряжение VGSлинейно нарастает с постоянной времени, определяемой CGS и резистором затвора RG. Поскольку уровень сигнала управления все еще находится ниже порога VGS(th), канал MOSFET остается закрытым.

На интервале времени t1–t2 ток стока ID начинает нарастать при достижении напряжением на затворе уровня VGS(th)(момент t1). Величина ID связана с сигналом управления через крутизну gfs (ID = gfs × VGS), и напряжение на затворе увеличивается до значения VGS1 = ID/gfs (t2). Поскольку оппозитный диод может заблокировать протекание тока только в момент времени t2, напряжение VDS до этого снижается несущественно. При t = t2 заряд затвора достигает значения QG2.

На данном интервале времени в транзисторе генерируется наибольшая часть потерь включения Eon. До тех пор пока ID< ILи часть тока IL все еще продолжает течь через оппозитный диод, уровень VDS не может стать намного ниже напряжения питания VDD. Разница VDD и VDS, отмеченная на рис. 13, в основном вызвана переходным динамическим падением сигнала на паразитных индуктивностях цепи коммутации.

Интервал времени t2–t3 соответствует полностью включенному транзистору. Когда оппозитный диод запирается, напряжение «сток–исток» падает до уровня насыщения VDS(on) = ID×RDS(on). Между моментами t2 и t3 ток стока и напряжение на затворе все еще связаны между собой через параметр крутизны, а величина VGS практически не меняется. После открывания MOSFET ток затвора IG разряжает емкость Миллера до уровня (QG3–QG2). При t = t3 на затворе остается количество заряда, равное QG3. Когда весь ток нагрузки IL начинает проходить через открытый канал MOSFET, начинается выключение оппозитного диода. Процесс обратного восстановления диода приводит к тому, что в течение времени trr ток стока ID превышает IL на величину IRR (ток обратного восстановления), и транзистор рассеивает дополнительную энергию, обусловленную зарядом Qrr.

Интервал времени t3–t4 соответствует омической области характеристики. В момент t3 транзистор включен, его рабочая точка прошла активную зону и достигла границы омической рабочей области. Сигнал управления VGS не связан больше с током ID через крутизну gfs, Накопление заряда затвора (QGtot–QG3) приводит к дальнейшему росту VGS, достигающего уровня выходного напряжения драйвера VGG.

Выключение

При выключении полевого транзистора все процессы происходят, как описано выше, но в обратном порядке. Заряд QGtotдолжен быть рассосан обратным током затвора, причем, в отличие от IGBT, силовые MOSFET не нуждаются в запирании отрицательным напряжением (VGSoff = 0). В процессе выключения необходимо разрядить только собственные емкости MOSFET до такого уровня, когда прекращается влияние носителей заряда на область канала.

Перенапряжение на стоке, отмеченное на рис. 13 в момент выключения, вызвано наличием паразитных индуктивностей в цепи коммутации, его уровень пропорционален скорости спада тока dID/dt.

Рис. 13. Эпюры токов и напряжений в режиме «жесткого» переключения MOSFET и IGBT с оппозитным диодом на активно-индуктивную нагрузку

Чем сильнее режим коммутации MOSFET отличается от «идеального жесткого переключения», тем более искаженной оказывается ступенчатая характеристика затвора.

Новейшие поколения MOSFET и основные направления их совершенствования

В силовой электронике в основном используются ключи с вертикальной структурой, в которых выводы затвора и истока располагаются на поверхности кристалла, а терминал стока — на его нижней стороне. При этом ток нагрузки проходит вертикально по чипу. Так называемые вертикальные полевые транзисторы с двойной диффузией (Vertical Double Diffused MOSFET), или VDMOSFET, появились на рынке в начале 80-х. Они до сих пор широко применяются, их совершенствование идет по пути уменьшения размера ячеек.

В зависимости от области применения и рабочего напряжения развитие технологии MOSFET идет по двум основным направлениям, первым из которых является Trench-Gate MOSFET (рис. 14) [13]. Структура транзистора с «канавочным» затвором впервые была представлена в 1997 г., ее совершенствование продолжается до сих пор.

Рис. 14.

слева — структура стандартного VDMOSFET;

справа — MOSFET с «канавочным» затвором (Trench MOSFET)

Подобно Trench IGBT, зоны изолированного затвора и канала расположены здесь вертикально, это позволяет заметно сократить расстояние, которое должны проходить электроны в n-области. В результате удается существенно снизить величину RDS(on), особенно в низковольтном диапазоне рабочих напряжений.

Наиболее заметный прогресс в улучшении характеристик проводимости полевых транзисторов был достигнут компанией Infineon в 1999 г., когда на рынке появились первые MOSFET с «суперпереходом» (Superjunction MOSFET) под торговой маркой CoolMOS. В этих ключах для снижения сопротивления канала при рабочих напряжениях в диапазоне 500–1000 В был использован принцип компенсации. Структура и принцип работы CoolMOS представлены на рис. 15 [11].

Рис. 15. Структура Superjunction MOSFET (CoolMOS)

С помощью многоступенчатой эпитаксии или боковой канавочной диффузии удается инжектировать высоколегированные проводящие «столбы» в слаболегированную n—-дрейфовую зону. Структурно они соединены с р-карманами. Степень легирования «столбов» выбирается таким образом, чтобы скомпенсировать n-примеси в дрейфовой области, в результате чего обеспечивается очень низкий эффективный уровень легирования.

В выключенном состоянии распределение поля является практически прямоугольным, блокирующая способность при этом определяется толщиной n-зоны. Легирование дрейфовой области может быть увеличено только до уровня, который компенсируется аналогичным количеством примесей в р-«столбе». Это позволяет переопределить степень взаимной зависимости величины запирающего напряжения и плотности легирования [3].

В результате толщина n—-дрейфовой области заметно снижается по сравнению с обычным MOSFET, а ее проводимость, соответственно, повышается за счет сильного легирования. Это означает, что сопротивление открытого канала RDS(on) не имеет больше степенной зависимости от рабочего напряжения, как было ранее. Использование принципа компенсации позволяет сделать связь RDS(on) и V(BR)DSS почти линейной, при этом потери проводимости высоковольтных MOSFET снижаются примерно в 3–5 раз. Площадь кристалла, потери переключения и емкость/заряд затвора уменьшаются соответственно; на рис. 16 [14] показана разница конструкций и характеристик стандартного и Superjunction MOSFET.

Чтобы распространить принцип «суперперехода» на MOSFET низковольтного диапазона, необходимо разработать гораздо более простую и дешевую технологию, чем та, что используется для производства высоковольтных транзисторов. Эта задача была решена компанией Infineon, разработавшей структуру OptiMOS, пригодную для производства ключей с рабочим напряжением до 300 В [15]. Вместо «столбов» в транзисторах OptiMOS используются изолированные «полевые пластины», встраиваемые в процессе эпитаксии. Они располагаются в канавках, вытравленных в n—-дрейфовой зоне и изолированных слоем оксида кремния. Пластины поочередно подключаются к области истока и затвора, выполненного из поликристаллического кремния (рис. 17) [15].

Рис. 17. Структура OptiMOS

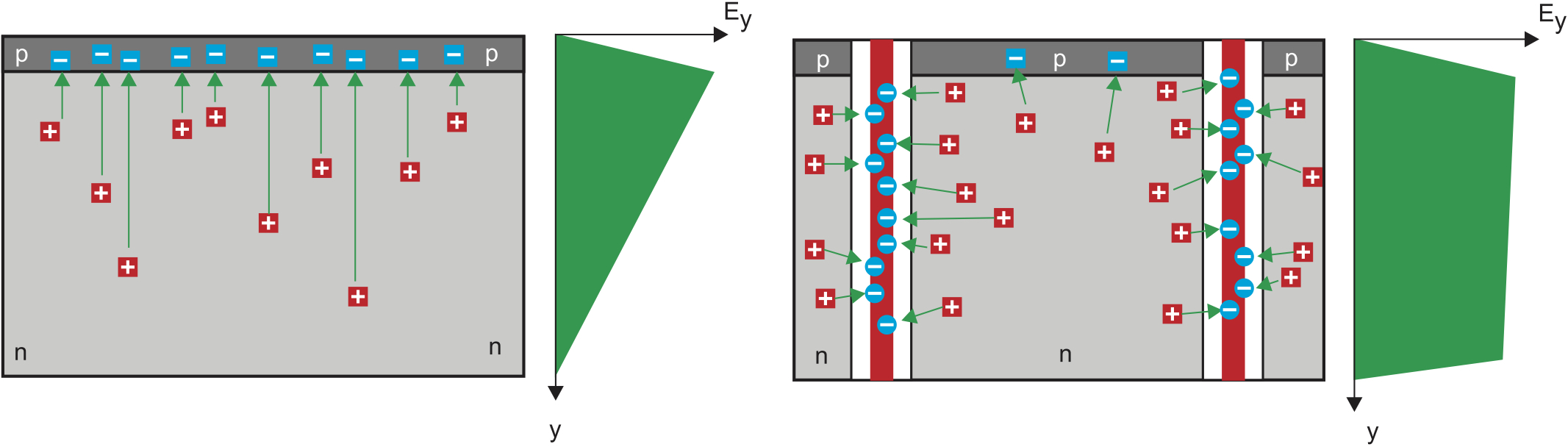

На рис. 18 [15] показан компенсационный эффект, оказываемый «полевыми пластинами», и характеристика напряженности поля по оси у в сравнении с обычным заблокированным p-n-переходом. Заряд р-типа «полевых пластин» компенсирует легирование n—-зоны, в результате чего оно может быть увеличено, как описано выше.

В выключенном состоянии треугольная форма поля в простой MOSFET-структуре становится почти прямоугольной, что позволяет снизить толщину n—-слоя. Повышение степени легирования и уменьшение размера дрейфовой области дают такие же преимущества, как и при использовании описанной выше концепции «суперперехода».

Наиболее перспективным направлением совершенствования силовых ключей является использование технологии карбида кремния (SiC), серийно внедряемой в производство ведущими производителями элементной базы. Широкому применению SiC-ключей на сегодня препятствует ограниченная нагрузочная способность и высокая цена. Основным путем расширения токового диапазона является увеличение размера чипа, однако это не лучший способ в отношении SiC-структур, поскольку он ведет к росту процента дефектных кристаллов и дальнейшему повышению стоимости готовых изделий.

Полная реализация возможностей SiC-технологии позволяет увеличить номинальный ток за счет ликвидации антипараллельных диодов (Schottky Barrier Diode, SBD) и использования обратной проводимости MOSFET, а также параллельного включения кристаллов без нарушения токового баланса.

Напряжение смещения у SiC PN-диодов относительно большое, поскольку карбид кремния является широкозонным материалом, и это создает высокие потери проводимости. Однако сравнительно высокое прямое напряжение внутреннего диода может быть снижено за счет использования эффекта обратной проводимости MOS-канала.

По-прежнему серьезным вопросом остается «биполярная деградация» SiC-структур. Проблемой SiC PN-диодов является расширение дефектной области после работы в режиме прямой проводимости, что приводит к росту сопротивления открытого канала и увеличению тока утечки. Компании ROHM удалось подавить этот эффект и подтвердить отсутствие каких-либо изменений в характеристиках тельного диода в течение 1000 ч, что было отмечено в материалах PCIM 2012.

Внутренние диоды SiC MOSFET имеют примерно такое же время обратного восстановления, как и SBD, а энергия динамических потерь у них меньше, чем у Si-MOSFET и кремниевых быстрых диодов (Si-FRD). Ток восстановления тельных диодов несколько увеличивается при температуре +125 °С, в то время как у SBD он остается примерно таким же, как и в нормальных условиях, однако энергия обратного восстановления у них намного меньше, чем у Si-FRD. Все сказанное позволяет создавать карбидокремниевые силовые модули без применения отдельных антипараллельных/оппозитных диодов.

При параллельном соединении полевых транзисторов с отрицательным температурным коэффициентом прямого сопротивления наибольший ток будет проходить через ключ с самым низким значением Ron, что в худшем случае приведет к его тепловому пробою. Однако в случае SiC MOSFET риск оказывается намного ниже, так как карбидокремниевые структуры имеют положительный температурный коэффициент (при напряжении включения Vgs = 18 В). Благодаря этому выравнивание токов параллельных SiC-ключей в статическом режиме происходит автоматически.

Тем не менее существует проблема небаланса токов затворов при включении. У кремниевых IGBT, имеющих низкое внутреннее сопротивление затвора, заметное влияние на распределение токов оказывает разница паразитных индуктивностей цепей управления. В худшем случае это может привести к разрушению кремниевых структур вследствие пусковых перегрузок и вызванных ими паразитных осцилляций.

В отличие от Si IGBT, карбидокремниевые транзисторы имеют относительно высокое внутреннее сопротивление затвора (несколько Ом). Благодаря этому приемлемое распределение токов управления параллельных чипов обеспечивается без применения дополнительных резисторов Rg. Данные свойства чипов SiC MOSFET делают их соединение очень простым без потери баланса токов стока и затвора, что позволяет исключить опасность возникновения теплового пробоя или паразитных резонансных колебаний.

Замена диодов Шоттки на внутренние диоды MOSFET позволяет увеличить номинальный ток модуля примерно на 50%. Компанией ROHM выпускается 100%-ный SiC MOSFET с номинальным током 180 А, напряжение насыщения при этом составляет 2,3 В (Ron = 12,8 мОм). Благодаря отсутствию «хвостового» тока и быстрым характеристикам восстановления SiC-структур, общее значение коммутационных потерь уменьшено на 75% по сравнению с аналогичным IGBT. Использование эффекта проводимости тельных диодов не снижает надежности работы модуля, испытания SiC MOSFET подтвердили отсутствие «биполярной деградации».

Заключение

Технологии изготовления SPT и Trench IGBT являются на сегодня наиболее отработанными, их преимущества перед стандартными ключами очевидны. Применение Trench-FS позволяет получить сверхнизкие потери проводимости, а SPT обеспечивают хороший компромисс характеристик проводимости и переключения. Оба типа модулей IGBT характеризуются высокой стойкостью к короткому замыканию и обладают эффектом самоограничения тока коллектора на уровне, не превышающем шестикратного номинального значения. В результате этого существенно снижается уровень перенапряжений при мгновенном срабатывании защиты от КЗ.

Повсеместное принятие экологических директив, в частности отказ от применения свинца, требуют кардинального изменения многих технологических процессов. Особенно это касается тонкопленочных технологий, где требуется разработка новых материалов металлизации. Именно растущие экологические требования привели к появлению так называемых «граничных» технологий IGBT, в частности субмикронной планарной (submicron-rule planar gate IGBT), которая, возможно, станет одной из базовых технологий будущего.

Одним из наиболее перспективных материалов для производства силовых ключей низкого и среднего диапазона мощности на сегодня представляется карбид кремния. Его применение позволяет резко снизить уровень динамических потерь, расширить температурный диапазон и отказаться от использования отдельных антипараллельных диодов.

- Arendt Wintrich, Ulrich Nicolai, Werner Tursky, Tobias Reimann. Application Notes for IGBT and MOSFET modules. SEMIKRON International. 2010.

- R. Higher Junction temperature in Power Modules — a demand from hybrid cars // PCIM Europe 2008. Conference Proceedings.

- Lutz J. Halbleiter-Leistungsbaulemente: Physik, Eigenschaften, Zuverlassigkeit // Springer Verlag Berlin Heibelberg 2006.

- Rusche W. Die vierte IGBT-generation. Modern IGBT ermoglichen Energieeinsparungen bei industrien Anwendungen. elektroniknet.de

- Dewar S., Linder S. Soft Punch Through (SPT) — Settling new Standards in 1200 V IGBT // PCIM Europe 2006. Conference Proceedings.

- Cammarata M., Kopta A. 1200 V SPT+ IGBT and diode Chip-Set for High DC-link Voltage Application // PCIM Europe 2009. Conference Proceedings.

- IGBT Modules Application Note. The 5th generation IGBT Chip. Mitsubishi, 12/2007.

- Takeda T., Kuwahara M., Kamura S. 1200 V trench gate NPT-IGBT (IEGT) with exellent low on-state voltage // ISPSD 1998. Conference Proceedings.

- Eckel H.-G. Potential of Reverse Conducting IGBT in Voltage Source Inverters // PCIM Europe 2009. Conference Proceedings.

- Buonomo S., Crisafulli V. ESBT technology in Industrial Converters: The Best Way to Cut Your Losses // PCIM Europe 2008. Conference Proceedings.

- Kapels H., Schmitt M., Kirchner U. New 900 V Class for Junktion Devices — A New Horison for SMPS and Renewable Energy Application // PCIM Europe 2008. Conference Proceedings.

- Stengl J.P., Tihanyi J. Leistuns-MOSFET-Praxis. Plaum verlag Munich. 2nd 1992.

- Gillberg J. Mixed Signal and Power Integration Packaging Solutions // Bodo’s Power Systems. 10/2009.

- Lutz J., Reimann T. Advanced design with MOSFET and IGBT Power Modules // PCIM Europe 2007. Conference Proceedings.

- Siemieniec R., Hirler F., Geissler D. Space-saving edge-termination structures for vertical charge compensation devices // EPE 2009. Conference Proceedings.

2 августа, 2010

2 августа, 2010