Особенности параллельного соединения модулей SiC MOSFET

Возможности SiC MOSFET по повышению тока (> 400 А) гораздо более ограничены по сравнению с Si IGBT, особенно если требуются компоненты в стандартных конструктивах или от нескольких поставщиков. Кроме того, физически меньшие корпуса, которые производятся крупными партиями, как правило, намного дешевле, чем большие, но выпускаемые малыми сериями. Однако при использовании параллельного соединения модулей прежде всего руководствуются техническими соображениями, и в случае SiC MOSFET это гораздо важнее, чем для IGBT, по следующим причинам:

- При установке на радиатор нескольких небольших корпусов обеспечивается гораздо лучшее распределение тепла и его отвод. Это позволяет получить большую токовую отдачу от более дорогих SiC MOSFET-модулей.

- Большие корпуса имеют более высокие распределенные индуктивности, как в силовом контуре, так и в цепях управления затвором, что определяется физической длиной цепи и использованием винтовых соединений для передачи высоких токов.

- Применение большого количества чипов делает крайне критичным требование к симметрии их расположения и выравниванию индуктивностей затворов. Решение этой задачи является очень трудным для стандартных конструктивов, имеющих ограниченные возможности.

- Из двух предыдущих пунктов понятно, как добиться большей скорости переключения и, следовательно, снизить потери и перепады напряжения при выключении при использовании корпусов меньших размеров.

Различия в параллельном соединении IGBT и SiC MOSFET

Тщательный анализ показывает, что, несмотря на более высокую скорость коммутации, в отношении параллельного соединения SiC MOSFET имеют некоторые преимущества по сравнению с IGBT.

- Транзисторы SiC MOSFET имеют более высокий положительный температурный коэффициент Rdson по сравнению с напряжением насыщения VCEsat Si IGBT. Это играет роль отрицательной обратной связи при статическом выравнивании токов. Если один из приборов принимает больший ток, то его чипы и сам модуль нагреваются сильнее, что увеличивает Rdson и, следовательно, уменьшает ток ключа. Такая отрицательная обратная связь снижает степень теплового дисбаланса.

- Коммутационные потери Si IGBT заметно растут с повышением температуры, и это положительно влияет на температурный небаланс. Более нагретый чип имеет большие потери, поэтому нагревается еще сильнее. SiC MOSFET демонстрируют незначительное увеличение коммутационных потерь при нагреве, что существенно снижает данный эффект.

- SiC MOSFET имеют более плавную прямую характеристику, то есть небольшие изменения напряжения на затворе в районе пороговой зоны оказывают меньшее влияние на ток стока, чем у эквивалентного Si IGBT. Это улучшает динамическое распределение токов.

- Статистический анализ приборов Infineon с Trench-затвором показывает, что с точки зрения распределения параметров модули с более высоким RDSon имеют меньшие коммутационные потери, что помогает отбирать партии компонентов по потерям.

Опыт работы с параллельным соединением на примере тестовой платформы

Рассмотрим некоторые аспекты тестовой платформы:

- Внутренняя топология модуля.

- Топология PCB силового каскада.

- Конструкция драйвера.

- Топология PCB-драйвера.

- Измерительные приборы.

- Статическое распределение токов.

- Динамическое распределение токов.

Внутренняя топология модуля

Параллельное соединение должно начинаться с анализа топологии мощных и сигнальных цепей внутри модуля. Внутренняя компоновка кристаллов и выводов модуля может быть выполнена таким образом, чтобы обеспечить одинаковость и симметрию мощных цепей и соединений затворов параллельных чипов. Это должно быть реализовано при сохранении низкой распределенной индуктивности контура коммутации. В общем случае контактный массив сетки в преобразователях, выполненных на основе PCB, позволяет гибко оптимизировать компоновку.

Топология PCB силового каскада

Топология модуля разделена на две симметричные половины. Для получения нужной симметрии силовая схема выполнена в виде зеркального отражения по осевой линии. Это необходимо для обеспечения равномерного распределения токов между чипами, входящими в модуль. Для каждого из четырех модулей была использована точная копия топологии, чтобы сохранить равномерное распределение токов между модулями. Также важно обеспечить низкую индуктивность внешнего контура коммутации, что достигается за счет перекрытия шин DC+ и DC–, выполненных в виде планарных медных слоев PCB с использованием развязывающих конденсаторов.

Схема драйвера

При использовании общего драйвера затвора для управления четырьмя параллельными модулями важно исключить протекание любых токов в сигнальной цепи истока. На рис. 1 на упрощенном примере с двумя модулями показано, как вспомогательное соединение истоков обеспечивает параллельный путь к силовой токовой цепи. Некоторые электроны, именуемые «подростковыми», потому что им нравится идти своей дорогой, могут течь по такой параллельной цепи сигнального истока. Этот ток может быть достаточно большим для того, чтобы вызвать осцилляции в цепи затвора и даже привести к повреждению и размыканию внутренних соединительных проводников модуля.

Схема, представленная на рис. 2, используется для уменьшения нежелательных циркулирующих токов. Она содержит синфазный дроссель, имеющий низкий импеданс по отношению к нормальным токам затвора, где входящий и выходящий токи равны, и высокий импеданс к нежелательным токам, проходящим только в цепи истока. Дополнительно для управления каждым затвором в драйвере предусмотрен отдельный усилительный каскад. Это позволяет создать сопротивление в подключении истока, но благодаря наличию конденсаторов любой ток, протекающий по этому пути, не влияет на форму сигнала управления затвором. Ситуация меняется при использовании обычного сопротивления истока, поскольку любой ток, проходящий по этому резистору, будет влиять на напряжение в цепи «затвор-исток», что снижет уровень сигнала управления и увеличивает возможность возникновения пульсаций затвора.

Топология платы драйвера

Модуль 6 мОм имеет двойные контакты для подключения выводов «затвор-исток» и двойные силовые контакты для подключения стока и истока. Это позволяет уменьшить индуктивность и улучшить распределение токов между чипами SiC MOSFET внутри модуля. Основная задача трассировки платы состоит в обеспечении симметрии подключения обеих пар цепей «затвор-исток». Далее необходимо гарантировать одновременное включение и выключение затворов всех четырех модулей. Это достигается с помощью структуры, называемой «дерево», обеспечивающей низкую индуктивность трасс «затвор-исток», имеющих одинаковую длину. Также должна быть симметричной и топология буферных каскадов для каждой пары подключений «затвор-исток». Измерения показали, что максимальная разница времен коммутации затворов не превышает 5 нс.

Измерительное оборудование

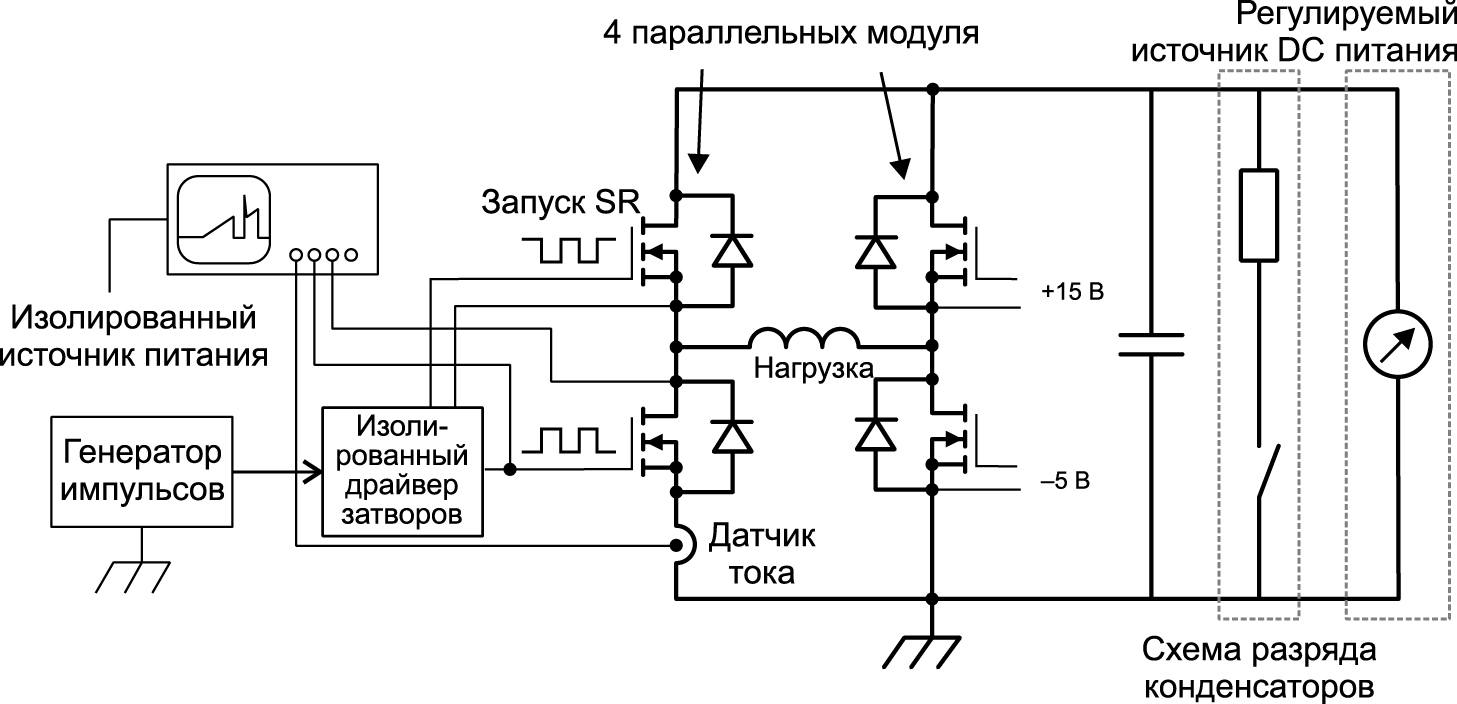

На рис. 3 показана схема, используемая для проведения так называемого двухимпульсного теста (DPT — Double Pulse Test). Важно измерить распределение токов в испытательной установке, построенной по схеме H-моста, чтобы прохождение токов и магнитные поля соответствовали конечному применению. Кроме того, нужно иметь возможность генерировать синхронные импульсы управления оппозитными ключами испытуемого устройства с «мертвым временем», длительность которого отвечает системным требованиям.

Для измерения токов стока и истока трассы DC-шины на печатной плате выполнены с отверстиями с обеих сторон для подключения петли Роговского. Это позволяет измерять ток в цепи DC–, который соответствует току стока нижнего ключа, и в цепи DC+, который отражает ток стока верхнего ключа. Также в установке предусмотрена возможность измерять баланс выходных токов между двумя наборами выходных контактов модуля.

Статическое распределение токов

На рис. 4 показан ток истока четырех нижних ключей в ходе теста DPT. Синхронное выпрямление использовалось для включения верхнего SiC MOSFET после окончания первого импульса, следующего за «мертвым временем», а не после второго импульса, который позволяет току перекоммутироваться на верхний встроенный диод. Небаланс токов четырех согласованных модулей составил ±3%. Отметим, что распределение токов ухудшается после второго импульса, когда MOSFET-транзистор не управляется и ток проходит только через встроенный диод.

Рис. 4. Тест DPT: форма токов четырех параллельных модулей (50 мкс/дел., 50 A/дел.).

Зеленая кривая — Vgs (5 В/дел.).

Синяя кривая — Vds (100 В/дел.):

а) обычный масштаб;

б) масштаб увеличен

Описанный начальный тест проводился с модулями, отобранными по величине RDS (разброс не более 2%). Также была выполнена проверка модулей с разбросом RDS 7%, при этом небаланс токов ухудшился на ±4%. Дополнительные испытания при высокой температуре и коммутации верхних ключей показали одинаково хорошие результаты. На рис. 4б представлены увеличенные эпюры сигналов, изображенных на рис. 4а.

Динамическое распределение токов

Измерения показали хорошее динамическое распределение токов как при включении, так и при выключении нижних транзисторов (рис. 5). Не наблюдалось никаких осцилляций тока, что также указывает на равномерное распределение токов между приборами во время включения и выключения. Испытания при различных температурах, измерения режимов верхних ключей и с 7%-ным разбросом RDS показали похожие характеристики.

Рис. 5. Тест DPT: выключение четырех параллельных модулей (200 нс/дел., 50 A/дел.).

Зеленая кривая — Vgs (5 В/дел.).

Синяя кривая — Vds (100 В/дел.):

а) обычный масштаб;

б) масштаб увеличен

Выравнивание токов в лаборатории и при серийном производстве

Лабораторные испытания продемонстрировали хорошее распределение токов на очень маленькой выборке модулей. Однако если устройство должно стать коммерческим крупносерийным продуктом, то необходимо рассчитать распределение токов для случайно выбранных модулей с нормальным распределением электрических параметров. Метод, используемый для этого, назван анализом Монте-Карло в честь знаменитого одноименного казино. Для анализа выбирают комплект из четырех модулей (каждый случайным образом), имеющих статистический производственный разброс значений потерь переключения и сопротивления RDS_on.

На основе этих параметров вычисляется ток в каждом модуле и оценивается температура их кристаллов. Поскольку потери переключения и величина RDS_on зависят от нагрева, для расчета конечного значения тока и температуры кристаллов в каждом модуле используется несколько итераций. Этот процесс можно повторить, например, для 50 000 комплектов случайно выбранных компонентов и вычислить нормализованное распределение Tj. В нашем случае результат представлял собой вариацию при ±3s от ±7С. Еще одна ошибка в расчетах вызвана тем, что существует перекрестная корреляция между RDS_on и коммутационными потерями Etot, когда приборы с меньшим значением RDS_on имеют тенденцию к более высокому Etot.

Заключение

В статье показано, что четыре параллельных модуля способны продемонстрировать хорошее распределение токов как в статических, так и в динамических условиях. С помощью анализа Монте-Карло компоненты могут быть выбраны случайным образом и при этом иметь хорошее распределение при массовом производстве. Необходимо позаботиться о подавлении осцилляций тока в цепях затворов, и, конечно же, разработчики должны следовать трем наиболее важным правилам параллельного соединения силовых полупроводников, а именно симметрии, симметрии и еще раз симметрии.

- Infineon AN 2017-41. Evaluation Board for CoolSiC Easy1B half-bridge modules.

- Infineon AN 2017-04. Advanced Gate Drive Options for Silicon Carbide (SiC) MOSFETs using EiceDRIVER.

- Infineon AN2014-12. EiceDRIVER™ 1EDI Compact Family. Techni-cal description.

- Infineon AN2018-09. Guidelines for CoolSiC MOSFET gate drive voltage window

- Infineon AN2017-14. Evaluation Board EVAL-1EDI20H12AH-SIC.

- Infineon AN2007-04. How to calculate and minimize the dead time requirement for IGBT’s properly.

- Infineon AN2017-46. CoolSiC 1200 V SiC MOSFET. Application Note.

17 мая, 2011

17 мая, 2011 12 мая, 2011

12 мая, 2011