Управление изолированными затворами MOSFET/IGBT, базовые принципы и основные схемы

Управление изолированным затвором: основные положения

В общем случае процесс перезаряда емкостей затвора может контролироваться сопротивлением, напряжением и током (рис. 1) [2].

Рис. 1. Управление затвором:

а) с помощью сопротивления;

б) напряжения;

в) тока

На практике чаще всего используется самый простой вариант (рис. 1а) с двумя раздельными резисторами для режимов включения и выключения, при этом одним из наиболее важных параметров является уровень «Плато Миллера», соответствующий плоской части характеристики затвора (рис. 2). Скорость и время коммутации задаются величиной RG при фиксированном напряжении управления VGG; чем меньше резистор затвора, тем быстрее происходит переключение. Отметим, что при использовании новейших поколений IGBT (например, Trench 4) может наблюдаться аномальная картина: при изменении RG в некотором диапазоне скорость выключения di/dt растет вместе с сопротивлением. Этот факт требует очень внимательного анализа, особенно при замене транзисторов предыдущих генераций [3].

Рис. 2. Ток и напряжение на затворе:

а) при включении;

б) выключении

К недостаткам «резистивного» метода управления можно отнести влияние разброса емкостей затвора на время коммутации и величину динамических потерь, а также упомянутую выше неопределенность зависимости di/dt от RG для некоторых типов современных транзисторов.

Прямое управление от источника напряжения (рис. 1б) устраняет данную зависимость, скорость коммутации в этом случае определяется фронтом прикладываемого к затвору сигнала dv/dt. Как следствие, на характеристике затвора наблюдается только незначительный участок «плато Миллера» или он отсутствует вообще. При использовании такого метода выходной каскад драйвера должен обеспечивать достаточный уровень напряжения и тока в течение всего времени коммутации. По сравнению со схемой 1а управление по напряжению требует применения гораздо более сложного и дорогого драйвера. Возможным компромиссом является использование комбинированного динамического метода контроля, при котором сигнал на затвор подается через резистор от регулируемого источника напряжения.

Токовое управление предусматривает использование источника «положительного» и «отрицательного» тока (рис. 1в), величина которого определяет скорость перезаряда затвора. Этот метод сопоставим с «резистивным», на практике он, как правило, используется в аварийных режимах для безопасного прерывания тока перегрузки или КЗ.

На рис. 2 показаны эпюры тока затвора iG и напряжения «затвор-эмиттер» VGE для схемы с «резистивным» контролем. Абсолютное максимальное значение напряжения управления VGG обеих полярностей определяется электрической прочностью изоляции затвора, для всех современных MOSFET/IGBT оно ограничено на уровне ±20 В. Эта величина не должна превышаться при всех условиях эксплуатации, включая аварийные режимы, что требует в ряде случаев принятия специальных мер.

Сопротивление открытого канала полевого транзистора RDS(on) и напряжение насыщения IGBT VCE(sat) снижаются при увеличении амплитуды сигнала управления. Рекомендуемая номинальная величина VGS(on) для MOSFET составляет 10 В, VGE(on) для IGBT — 15 В, все статические и динамические характеристики полупроводников нормируются при данных условиях. При этих значениях обеспечивается приемлемый компромисс между мощностью рассеяния, пиковым током включения и стойкостью к КЗ. Есть также отдельный класс полевых транзисторов, управляемых непосредственно от логических элементов (logic-level MOSFET), они включаются при VGS(on) = +5 В.

Как показано на рис. 2, блокирование IGBT должно производиться отрицательным напряжением, рекомендуемые уровни VGE_off (в зависимости от мощности прибора): -5/-8/-15 В. В течение всего времени toff (даже если напряжение управления достигает величины VGE(th)) это позволяет поддерживать отрицательный ток затвора, что необходимо для быстрого и безопасного отключения.

В некоторых источниках рекомендуется использование нулевого напряжения выключения VGEoff = 0. Однако в мощных полумостовых каскадах в этом случае возникает опасность появления сквозного тока при обратном восстановлении антипараллельного диода вследствие обратной связи по dvCE/dt (рис. 3). Крутой фронт напряжения «коллектор-эмиттер» vCE2 при восстановлении D2 приводит к образованию тока смещения iv (iv = CGC2 × dvCE/dt) через емкость Миллера, который создает падение напряжения на RG (или RGE/RG). При этом уровень наведенного на затворе сигнала может превысить порог VGE(th), вследствие чего транзистор Т2 перейдет в активную зону. Генерируемый в процессе обратного восстановления сквозной ток создает дополнительные потери мощности на ключах Т1 и Т2.

Рис. 3. Сквозной ток в полумостовом каскаде IGBT из-за ложного включения Т2 вследствие обратной связи по dv/dt:

а) электрическая схема;

б) эпюры тока и напряжения

Сказанное выше не относится к мощным MOSFET-ключам, хотя ложное срабатывание из-за наличия паразитных элементов может произойти и в них. При коммутации MOSFET точно так же возникает ток смещения, проходящий через емкость CDS к базе паразитной биполярной n-p-n-структуры. Если падение напряжения на резисторе RW в поперечном р-кармане (рис. 4) превысит пороговый уровень отпирания n-p-n-транзистора, то он откроется, и это может привести к полному разрушению MOSFET вследствие локального перегрева.

Рис. 4. Ячейка MOSFET:

а) структура с основными паразитными элементами;

б) эквивалентная электрическая схема

Однако паразитное включение полевого канала при VGS = 0 снижает величину dvDS/dt в заблокированном состоянии и таким образом ослабляет негативный эффект от наличия паразитного транзистора. Кроме того, при этом уменьшается значение dv/dt в момент запирания внутреннего диода MOSFET и, следовательно, исключается возможность его повреждения вследствие динамического стресса.

В практических схемах драйверов MOSFET иногда применяется режим запирания нулевым напряжением на время коммутации диода и отрицательным сигналом в статическом состоянии.

Ток и мощность управления

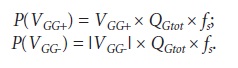

Общая мощность PGavg, необходимая для управления MOSFET/IGBT, определяется на основе значения заряда затвора QGtot, приводимого в технических характеристиках:

Пиковый ток затвора зависит от напряжения управления и сопротивления в цепи затвора:

Формула позволяет получить идеальные значения; в реальности ток всегда меньше, поскольку он ограничен выходным импедансом драйвера, индуктивностью цепи управления и входными емкостями MOSFET/IGBT. Чем меньше резистор затвора RG, тем больше разница расчетных и реальных значений IGM.

Для определения мощности управления (на один канал) используются следующие формулы):

Параметры драйвера и динамические характеристики

Как было сказано выше, статические и динамические характеристики силовых ключей во многом определяются параметрами схемы управления (табл. 1).

| Характеристика | VGG+ | VGG- | RG |

| RDSon, VCEsat | > | — | — |

| ton | > | < | < |

| Eon | > | — | < |

| toff | < | > | < |

| Eoff | — | > | < |

| Пиковый ток включения транзистора* | < | — | > |

| Пиковый ток выключения диода* | < | — | > |

| Пиковое напряжение при включении транзистора* | — | < | > |

| di/dt | < | < | >** |

| dv/dt | < | < | > |

| Ток самоограничения ID, IC | < | — | — |

| Стойкость к КЗ нагрузки | > | — | < |

Примечания: «<» — увеличение; «>» — уменьшение; «-» — нет влияния; * — в режиме «жесткого переключения» при активно-индуктивной нагрузке; ** — не постоянно в диапазоне изменения RG при выключении.

Прямые характеристики RDSon, VCEsat

Зависимость прямых характеристик MOSFET и IGBT от параметров управления может быть определена на основе их выходных характеристик. На рис. 5 это поясняется на примере графиков, взятых из спецификаций модулей SEMITRANS компании SEMIKRON.

Время коммутации и энергия потерь (ton, toff, Eon, Eoff)

Напряжение управления и сопротивление в цепи затвора влияют на время включения ton = td(on)+tr, выключения toff = td(off) + tf и продолжительность «хвостового» тока t. Поскольку для включения IGBT емкости затвора необходимо зарядить до порогового уровня, время перезаряда между циклами коммутации (задержка включения и выключения td(on) и tdff)) будет снижаться при уменьшении резистора RG.

С другой стороны, время нарастания и спада тока (tr/tf) и, следовательно, значительная часть энергии потерь Eon и Eoff в высокой степени зависят от параметров цепи управления: VGG+, VGG- и RG. В технических характеристиках IGBT приводятся графики зависимости времени коммутации и энергии переключения от сопротивления затвора; в большинстве случаев они нормированы для номинального тока и режима «жесткой» коммутации активно-индуктивной нагрузки (рис. 6).

Рис. 6. Зависимость от RG: а) временных характеристик IGBT; б) потерь переключения (режим «жесткой коммутации», активно-индуктивная нагрузка; Tj = +125 °C, Vce = 600 B, IC = 75 A, VGE = ±15 В)

Динамические характеристики оппозитного диода

На графике Eon, приведенном на рис. 6б, учтено влияние процесса обратного восстановления оппозитного диода на ток коллектора и потери включения IGBT.

Время нарастания tr тока коллектора/стока (ID/Ic) снижается с ростом тока затвора (при увеличении VGG+ или уменьшении RG). При этом также возрастает скорость коммутации dIF/dt оппозитного диода, его заряд Qrr и пиковый ток восстановления IRRM. Все эти зависимости приводятся в спецификациях силовых ключей (рис. 7 и 8). В свою очередь, увеличение Qrr и IRRM приводит к росту потерь выключения диода.

Рис. 7. Заряд Qrr:

а) и пиковый ток восстановления IRRM;

б) оппозитного диода IGBT модуля SKM100GB123D в зависимости от скорости изменения тока диода dlF/dt

Рис. 8. Потери выключения EoffD оппозитного диода в зависимости от RG при включении транзистора

Поскольку повышение dIF/dt вызывает соответствующее изменение Qrr и IRRM, а IRRM в свою очередь добавляется к IC (ID), то пиковый ток транзистора и его потери включения увеличиваются пропорционально скорости включения (рис. 6).

При увеличении напряжения выключения VGG- (или снижении RG) начинает расти ток выключения затвора. Как показано на рисунке 6а, время спада tf при этом снижается, соответственно растет di/dt. Негативным следствием увеличения скорости коммутации является появление опасных коммутационных всплесков напряжения на распределенных индуктивностях Ls силовых цепей, амплитуда которых пропорциональна di/dt и Ls. Более подробно вопросы нормирования параметров цепей управления рассмотрены в [8, 9, 10].

Базовая схема управления затвором

На рис. 9 приведена блок-схема высококачественного устройства управления полумостовым каскадом MOSFET/IGBT. В дополнение к базовым функциям такой драйвер блокирует одновременное включение транзисторов стойки (функция TOP/BOTTOM Interlock), а также осуществляет защиту от перегрузок, мониторинг основных режимов и нормирование формы входных импульсов.

Рис. 9. Базовая структура полумостового каскада со схемой управления, осуществляющей функции защиты и мониторинга

Устройство обрабатывает сигналы управления ключами верхнего (ТОР) и нижнего (ВОТ) уровня, полученные от центрального процессора, осуществляет их потенциальную изоляцию, доводит амплитуду и мощность до уровня, необходимого для перезаряда затвора на частоте коммутации. Кроме того, схема защиты анализирует аварийные состояния и формирует обобщенный сигнал неисправности, который передается во входной низковольтный каскад.

В маломощных и недорогих драйверах может отсутствовать гальваническая развязка, в этом случае для передачи сигнала управления на затвор ТОР транзистора используется каскад сдвига уровня. Как правило, в подобных устройствах питание верхних каскадов осуществляется от бутстрепных емкостей. Самая простая схема без потенциальной изоляции и сдвига уровня применяется для управления одиночными ключами нижнего уровня (например, тормозным чоппером). В этом случае задачей драйвера является только обеспечение достаточного напряжения и тока затвора.

Каскад управления затвором является ключевым узлом драйвера, определяющим его временные характеристики, требования к изоляции, уровень и мощность сигнала VGE. Он также осуществляет защиту ключа от перегрузки по току и КЗ, в ряде случаев в устройство может быть интегрирована цепь активного ограничения напряжения на коллекторе. На рис. 10 приведена базовая схема выходного каскада с раздельными цепями включения (положительным напряжением VGG+) и выключения (отрицательным напряжением VGG-) затвора. В двухтактной («пушпульной») схеме обычно используется комплементарная пара полевых или биполярных транзисторов.

Рис. 10. Выходной каскад драйвера с раздельными цепями управления включением и выключением затвора

Резистор затвора на рис. 10 разделен на две составляющие: RGon и RGoff, что позволяет независимо оптимизировать динамические характеристики в режиме включения и выключения. Такая схема также ограничивает уровень сквозного тока в цепи VGG+/VGG-, возникающего при коммутации MOSFET. Если у драйвера есть только один выход, то для разделения на RGon и RGoff используется диод, подключенный последовательно с одним из резисторов [9].

Установка резистора утечки RGE (10-100 кОм) не является обязательной, однако это полезно, например, для защиты затвора от статического разряда в тех случаях, когда выход драйвера подключается с помощью разъема и есть вероятность пропадания контакта. Кроме того, использование RGE позволяет предотвратить нежелательный заряд емкостей затвора, который может произойти в режимах, характеризующихся высоким импедансом цепи управления (коммутация, выключенное состояние, повреждение источника питания драйвера).

Низкоиндуктивная емкость (С) на выводах питания драйвера работает как буфер, позволяющий снизить динамическое выходное сопротивление драйвера и обеспечить высокое пиковое значение тока затвора при коммутации. Она также выполняет полезную функцию при пассивном ограничении напряжения на затворе с помощью диода Шоттки, подключаемого между затвором и цепью VGG+.

Кроме сказанного выше, при проектировании выходного каскада драйвера необходимо принимать во внимание следующие аспекты:

- Цепь управления затвором должна иметь минимальную индуктивность, для чего ее рекомендуется выполнять витой парой, особенно если длина соединения превышает 5 см.

- Следует минимизировать влияние силовых линий на цепь затвора, оно может вызваться паразитной обратной связью по выводу эмиттера или контуру заземления.

- Следует исключить трансформаторные и емкостные связи цепей затвора и коллектора, наличие которых может привести к возникновению паразитных осцилляций.

Как видно из блок-схемы, представленной на рис. 9, в состав высококачественного устройства управления входит входной фильтр, блок нормирования формы импульсов, генератор «мертвого времени» и подавитель коротких импульсов. Все эти узлы не только вносят временную задержку, но и влияют на глубину модуляции, что необходимо учитывать при проектировании системы [8].

Защитные и контрольные функции драйверов

Защита силовых ключей от разного рода аварийных ситуаций является одной из важнейших функций схемы управления. Для ее реализации драйверы снабжаются блоками оперативного мониторинга перегрузки по току и КЗ, перенапряжения на коллекторе и затворе, перегрева, а также падения напряжения управления VGG+/VGG-.

Защита от перегрузки по току

Измерение тока коллектора/стока производится с помощью резистивных шунтов, токовых трансформаторов, индукционных сенсоров и т. д. Одним из самых распространенных методов мониторинга состояния токовой перегрузки является измерение напряжения насыщения транзистора. Выход из насыщения (Desaturation), при котором величина VCEsat достигает определенного порога, рассматривается как аварийная ситуация. При этом драйвер блокирует силовые транзисторы и формирует сигнал неисправности ERROR, который через изолирующий барьер передается на входной каскад и далее на контроллер. Интеллектуальные модули высокой степени интеграции (например, SKiiP компании SEMIKRON) имеют в своем составе датчики тока, информация с которых используется схемой защиты вместе с напряжением насыщения, что позволяет сократить время реакции и отключить IGBT при меньшем уровне перегрузки.

Защита от перенапряжения на затворе

Функцию ограничения напряжения на затворе рекомендуется реализовывать в любом драйвере, независимо от наличия аварийной ситуации. Кроме защиты затвора от пробоя, это позволяет ограничить ток КЗ. Подробнее данный вопрос будет рассмотрен далее.

Защита от перенапряжения на коллекторе (стоке)

Ограничение напряжения на силовых терминалах может осуществляться самим модулем (большинство MOSFET обладает стойкостью к лавинному пробою), внешними пассивными снабберами, а также активными цепями, переводящими транзистор в линейный режим при возникновении опасного перенапряжения.

В ряде интеллектуальных модулей (например, SKiiP) реализована функция запрета коммутации при достижении напряжением DC-шины порогового уровня. Эта опция не способна защитить от внешних перенапряжений, однако она позволяет исключить влияние коммутационных выбросов в критических режимах, что существенно повышает надежность работы преобразовательного устройства. Мониторинг напряжения питания производится «квази-изолированным» датчиком на основе высокоомного дифференциального усилителя, передающего аналоговый сигнал, пропорциональный VDC, на схему управления. Если величина VDC превышает заданный уровень, силовые транзисторы отключаются, и схема защиты формирует сигнал неисправности. В ряде случаев параллельно цепи питания инвертора устанавливается тормозной чоппер, активно разряжающий конденсаторы звена постоянного тока при опасном увеличении напряжения. Такая схема чаще всего применяется в приводах, где используется режим динамического торможения (электротранспорт, лифты и т. д.).

Защита от перегрева

Температура силовых кристаллов, а также изолирующей подложки рядом с чипами, корпуса модуля и радиатора может быть определена расчетным методом или с помощью сенсоров. Если термодатчик гальванически изолирован, то его выходной сигнал передается на схему управления и используется для отключения силового каскада и формирования сигнала неисправности.

Защита от падения напряжения управления VGG+, VGG- (Under Voltage LockOut, UVLO)

Падение напряжения питания выходного каскада драйвера и, соответственно, уровня VGE нежелательно по многим причинам. В первую очередь при этом возрастает опасность перехода ключа в линейный режим работы и резкого увеличения рассеиваемой мощности. Кроме того, в этом случае теряется управляемость: транзистор не может быть полностью открыт или заблокирован. Мониторинг критического состояния производится путем измерения величин VGG+, VGG- с последующим отключением силового каскада при их снижении до опасного уровня.

Временные характеристики и предотвращение сквозного тока

Подавление коротких импульсов (Short Pulse Suppression, SPS)

При использовании импульсных трансформаторов или оптопар для гальванической

изоляции контрольных сигналов очень важно обеспечить защиту канала управления от воздействия помех. Отличительными признаками шумовых сигналов являются их амплитуда и длительность, которые, как правило, гораздо меньше, чем у импульсов, формируемых контроллером. Для подавления помех в состав драйверов SEMIKRON включен фильтр, не пропускающий сигналы длительностью меньше 0,2-0,5 мс.

«Мертвое время» tdt, защита от одновременного включения (Interlock) и время блокирования tbl

Для предотвращения сквозного тока в инверторах напряжения драйвер должен исключать одновременное включение транзисторов ТОР и ВОТ полумоста. Для этой цели используется функция Interlock, имеющаяся в подавляющем большинстве современных драйверов. Эта опция не применяется в инверторах тока и трехуровневых инверторах напряжения, где открывание ключей одной стойки необходимо в некоторых рабочих состояниях.

После запирания одного из ключей полумоста включение оппозитного транзистора должно происходить с некоторой задержкой. Время tdt, называемое «мертвым», учитывает задержку включения и выключения драйвера и транзистора, в течение tdt должны закончиться все переходные процессы. В зависимости от типа транзистора и области применения «мертвое» время находится в диапазоне 2-8 мкс. В первую очередь это относится к режиму «жесткой» коммутации, для работы в резонансных режимах значение tdt снижают вплоть до 0.

При использовании напряжения насыщения VCEsat в качестве критерия токовой перегрузки схема защиты должна быть блокирована на некоторое время tbl, необходимое для полного отпирания транзистора. Чтобы реакция на неисправность была максимально быстрой, рекомендуется изменять опорный сигнал схемы защиты Vref по такому же динамическому закону, по которому происходит спад напряжения «коллектор-эмиттер» VCE. Как видно на рис. 11, в первый момент после открывания ключа величина VCE намного выше установившегося значения VCEsat, определяемого прямой характеристикой.

Рис. 11. Динамическое насыщение IGBT и пороговый уровень напряжения Vref

При использовании динамического опорного напряжения время блокирования можно существенно снизить tmin. Чтобы удовлетворить требованиям области безопасной работы для режима короткого замыкания (SC-SOA), tbl ни при каких условиях не должно превышать предельно допустимой длительности КЗ (для последних поколений IGBT максимальное значение tSCmax составляет 6 мкс) (рис. 12).

Рис. 12. Возможные сценарии выхода транзистора из насыщения

Передача и усиление сигнала управления

Сигналы управления, формируемые центральным процессором, информация о состоянии вторичных каскадов (статус и ошибка), а также выходные сигналы датчиков (ток, напряжение, температура, напряжение DC-шины) должны передаваться между узлами драйвера, имеющими различный потенциальный уровень.

В подавляющем большинстве выпускаемых драйверов для потенциальной развязки используются импульсные трансформаторы, оптопары или «квази-потенциальные» изоляторы, к которым относятся каскады сдвига уровня с бутстрепным питанием каналов верхнего уровня.

На рис. 13 показаны базовые схемы передачи сигналов управления. Самая сложная конфигурация, используемая в преобразователях высокой мощности (рис. 13а), обеспечивает потенциальную развязку импульсов S и энергии управления Р по каждому каналу. Такая топология является наиболее предпочтительной, она отличается высокой помехозащищенностью и минимальным уровнем взаимного влияния ключей.

Рис. 13. Принципы передачи энергии управления:

а) полная схема для применений высокой мощности;

б) общий источник питания для драйверов ключей ВОТ;

в) принцип бутстрепного питания;

г) принцип сдвига уровня (STOP, SBOT: сигналы управления для ключей TOP/BOT; PTOP, PBOT: передача энергии управления для ключей TOP/BOT)

Вариант на рис. 13б содержит раздельные каналы потенциальной изоляции для всех драйверов ТОР и только один общий изолятор для драйверов нижнего уровня ВОТ. Как правило, такая структура применяется в маломощных схемах, кроме этого, она широко распространена в интеллектуальных модулях (IPM).

Принцип «бутстрепного» питания, позволяющий передавать энергию управления транзисторам верхнего плеча без потенциальной изоляции, поясняется на рис. 13в. На рис. 13г показан каскад сдвига уровня, транслирующий контрольный сигнал STOP без гальванической развязки посредством высоковольтного источника тока. Подобная топология, как правило, применяется в монолитных интегральных схемах драйверов.

Наиболее важным требованием, предъявляемым к каскадам гальванической развязки, является высокая статическая прочность изоляции (2,5-4,5 кВ в соответствии со стандартами) и иммунитет к наведенным фронтам dv/dt (15-100 кВ/мкс). Последнее требование выполняется за счет применения изоляционных барьеров со сверхнизкой проходной емкостью (1-10 пФ) между первичными и вторичными каскадами. Это позволяет минимизировать или даже полностью устранить влияние помех, вызванных коммутационными токами смещения.

![Эквивалентные емкости полумостового каскада с потенциальной изоляцией: емкость между первичным и вторичным каскадом канала ВОТ; емкость между первичным и вторичным каскадом канала ТОР; емкость между вторичными каскадами каналов ТОР и ВОТ] Эквивалентные емкости полумостового каскада с потенциальной изоляцией](https://power-e.ru/wp-content/uploads/50_pic14.jpg)

Рис. 14. Эквивалентные емкости полумостового каскада с потенциальной изоляцией

(Cps1: емкость между первичным и вторичным каскадом канала ВОТ; Cps2: емкость между первичным и вторичным каскадом канала ТОР; Css: емкость между вторичными каскадами каналов ТОР и ВОТ]

Сигналы управления и обратной связи

В таблице 2 приведены характеристики основных методов передачи сигналов управления и обратной связи с потенциальной изоляцией и без нее, используемые в драйверах MOSFET/IGBT.

| Характеристика | Импульсный трансформатор (с магнитным сердечником), трансформатор без сердечника | Оптопара | Волоконно-оптическая линия связи |

| Принцип потенциальной изоляции | Магнитный | Оптический | Волоконно-оптический |

| Гальваническая изоляция | + | + | + |

| Направление передачи | Двунаправленный | Двунаправленный | Двунаправленный |

| Разброс времени задержки | Низкий | Высокий | Высокий |

| Реакция на воздействие магнитного поля | + | — | — |

| Реакция на воздействие электрического поля | — | — | — |

| Иммунитет к dv/dt | 35…50…100 кВ/мкс | 15-25 кВ/мкс | ND |

Информация с датчиков тока, напряжения, температуры может транслироваться на схему управления через те же изолирующие барьеры с помощью широтно-импульсной модуляции.

В таблице 3 приведен обзор наиболее известных принципов изолированной передачи энергии управления к драйверу.

| Характеристика | Сетевой трансформатор 50 Гц | Низковольтные каскады | Высоковольтные каскады | Бутстрепная схема |

| Источник питания | ||||

| Принцип потенциальной изоляции | Магнитный (трансформаторная развязка) | Высоковольтный p-n-переход | ||

| Гальваническая изоляция | + | + | + | — |

| Питание | Вспомогательный или основной источник питания | Вспомогательный источник питания | DC-шина | Рабочее напряжение транзистора ВОТ |

| АС-частота | Низкая | Очень высокая | Средняя | Средняя (частота ШИМ) |

| Требования по сглаживанию | Высокие | Очень низкие | Низкие | Низкие |

| Ограничение скважности | Нет | Нет | Нет | Есть |

Твердотельные и интегральные микросхемы драйверов

В большинстве случаев устройства управления затворами строятся на базе интегральных схем, доступных в различных конфигурациях: одиночной, полумостовой и трехфазной.

Как правило, они выполняют следующие функции:

- формирование импульсов управления затвором;

- мониторинг напряжения насыщения (VCEsat, VDSon) или сигнала, снимаемого с резистивного шунта для индикации состояния перегрузки;

- мониторинг падения напряжения управления (UVLO) для исключения перехода силового транзистора в линейный режим работы;

- формирование сигнала ошибки;

- формирование «мертвого времени»;

- бутстрепное питание верхнего каскада драйвера;

- блокировка входных импульсов;

- потенциальный сдвиг уровня сигнала ТОР в неизолированных драйверах.

Современные твердотельные микросхемы драйверов производятся на основе технологии SOI (Silicon On Insulator), в которой полностью подавлен эффект защелкивания благодаря изоляции каждого активного элемента структуры. Это позволяет расширить диапазон рабочих температур, повысить надежность каскада сдвига уровня, улучшить иммунитет к dv/dt и стойкость к наведенным помехам отрицательной полярности.

Еще одной возможностью реализации интегрального драйвера MOSFET/IGBT является комбинация быстрой оптопары с выходным каскадом. Для создания законченного устройства управления в состав изделия необходимо включить DC/DC-преобразователь или бутстрепную схему для питания каналов ТОР, а также элементы обвязки.

В условиях растущего многообразия функций и алгоритмов защиты драйверов затворов к элементам, ставшим обязательными для устройств управления, добавляются и новые узлы. К ним относятся, например, блок формирования входных импульсов, фильтр подавления шумов, генератор «мертвого» времени, память схемы защиты, управление DC/DC-конвертером источника питания и т. д. Все описанные функции реализованы в специализированных интегральных схемах, используемых в драйверах SEMIKRON.

- Arendt Wintrich, Ulrich Nicolai, Werner Tursky, Tobias Reimann. Application Notes for IGBT and MOSFET modules. SEMIKRON International. 2010.

- Scheuermann U. Paralleling of Chips — From the Classiacl «Worst Case» Consideration to a Statistical Approach // PCIM Europe 2005. Conference Proceedings.

- Bruckmann M., Sigg J. Reihenschaltung von IGBT in Experiment und Simulation // Conference Proceeding. Freiburg. 1995.

- Bruckmann M. Einsatz von IGBT fur Hochleistungsstromrichter. Bad Nauheim. 1998. Proc.

- Gerster Ch., Hofer P., Karrer N. Gate-control Strategies for Snubberless Operation of Series Connected IGBTs. // PESC’96. Baveno. Proc. Vol. II.

- Ruedi H., Kohli P. Dynamic Gate Control (DGC) — A New IGBT gate Unit for High Current IGBTs // PCIM Europe 1995. Conference Proceedings.

- Helsper F. Adaptation of IGBT Switching Behaviour by Means of Active gate Drive Control for Low and Medium Power // EPE 2003. Conference Proceedings.

- AN3 AN-7002: Connection of Gate Drivers.

- AN5 AN-7003: Gate resistors.

- AN6 AN-7004: IGBT Driver Calculation.

7 февраля, 2017

7 февраля, 2017